-

万博Ansys软件在模拟仿真学生的过程中取得了很大的成功,这使得Ansys软件在模拟仿真方面取得了很大的进步。

-

万博Ansys软件在模拟仿真学生的过程中取得了很大的成功,这使得Ansys软件在模拟仿真方面取得了很大的进步。

-

万博Ansys软件在模拟仿真学生的过程中取得了很大的成功,这使得Ansys软件在模拟仿真方面取得了很大的进步。

万博ANSYS的博客

2021年8月6日

PCB设计规则:布线和串扰

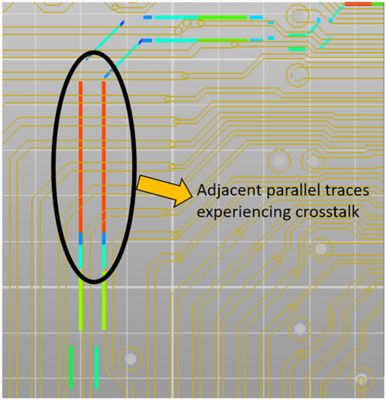

当今的电子设备市场需要小型化的印刷电路板(pcb),将多种高速功能集成在一块电路板上。这导致设计师有痕迹路由非常接近对方,以优化包装和空间。这种接近可能会导致无意的电磁场耦合,这种现象我们称之为串扰(见图1)。

尽管紧密封装可能是不可避免的,但某些PCB设计规则与PCB上的布线/路由有关,不应违反这些规则,以避免潜在的串扰和电磁干扰/兼容性(EMI/EMC)问题。我们已经通过了一些PCB设计规则在本博客系列的第1部分,但让我们在第二部分(也是最后一部分)中看看其他一些重要的设计准则。我们也会看看如何万博Ansys SIwave使pcb级模拟能够在违反这些准则时识别潜在的EMI/EMC问题区域。

(在以下章节中,短语“关键网”是指PCB上的走线,根据PCB的应用,可能参考高速时钟/数据线,重要传感线等。)

图1:PCB上有潜在串扰问题的相邻走线示意图。

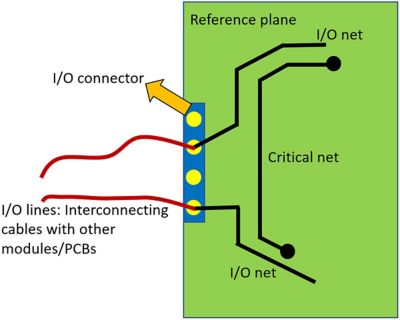

规则1:关键网络靠近I/O网络

重要的是要查看与I/O线路相关的关键网络的路由,因为噪声很容易通过这些I/O线路离开或进入电路板(见图2),并将PCB与系统中的其他PCB或模块连接到外部世界。

图2:关键网络和I/O网络相互靠近路由的场景说明。

通过I/O线进入电路板的任何噪声都有可能耦合到承载重要数据/时钟信号的关键网络,这基本上是PCB的抗扰度方面(图3a)。以类似的方式,任何由关键网携带的高速信号都可以耦合到I/O网,最终通过从板上下来的I/O线到达外部世界,并进入系统中的其他模块。原则上,这将是PCB的排放方面(图3b)。

图3a(左)和3b:由于靠近关键网络和I/O网络而引起的潜在EMI/EMC问题

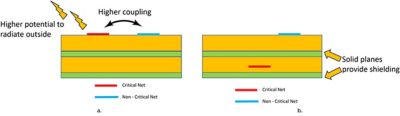

规则2:暴露的关键跟踪长度

在波长较短的高速PCB (> 100MHz)上,任何临界网(见图4a)的电长度都足以使其成为有效的散热器,特别是当暴露在顶层或底层时。这种不需要的辐射可以耦合到任何相邻的走线,甚至耦合到靠近走线的组件中存在的电缆。我们建议将关键网埋在PCB内层的实心平面之间,如图4b所示。这有助于包含来自走线的场,并避免以串扰或EMI的形式出现任何无意的耦合。如果不可避免地暴露关键网,暴露部分的长度应尽可能短。这是因为较短的暴露线的长度将有较少的倾向辐射,因为他们将是低效的天线,如果他们是电小。

图4a(左)和b:在实平面之间暴露或埋设临界网的示意图

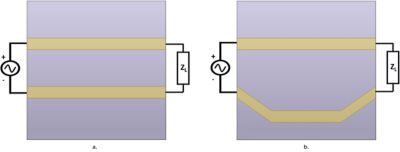

规则3:关键差分网匹配

理论上,差分对携带的信号大小相等,极性相反,因为差分对产生的电磁干扰可以抵消或忽略不计。但是,这只有在对中的走线长度相等并且尽可能对称地彼此靠近时才有效。违反这些中的任何一个都可能产生共模噪声和EMI问题。这是一个非常值得关注的问题,特别是对于携带高频关键信号的差分网,因为电磁干扰增加了所携带信号的频率。图5显示了IC封装和电路板上的出口点(连接器)之间的关键差分对路由的正确/错误方法的几个示例。

图5:参考平面中存在分裂时的返回电流路径

临界差分网络匹配:仿真及与实际试验要求的关系

在图6a和6b中的PCB示例中,我们有一个简单的PCB上的差分对以两种不同的方式路由:分别是对称和不对称。在这两种情况下,在SIwave中,它们一端用差分电压源激发,另一端用负载终止。

图6a(左)和b:在PCB上布线的差分对示例

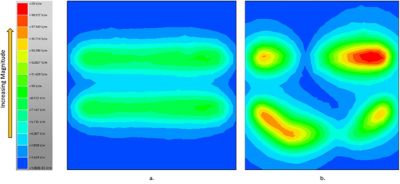

我们对两个案例都进行了近场分析。在差分对对称布线的PCB中,近场电平低于它们不对称布线的情况,如图7a和7b所示。

图7a(左)和b:近场@ 597.45 MHz,对称和非对称差分对网

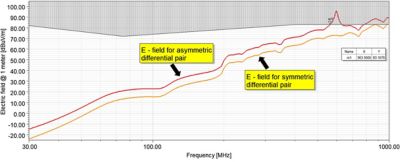

假设我们要根据EMI/EMC法规AIS 004(在印度)或UNECE R10(在欧洲)的辐射排放要求测试该PCB。图8显示了在30 MHz -1 GHz频率范围内,该PCB在1米距离上模拟远场的对比分析。请注意,不对称差分对的情况下增加了约8至10 dB的发射水平,也导致563.50 MHz及以上的不合规。

图8:1米辐射排放比较

SIwave在PCB级上的模拟能够早期识别此类EMI问题,这有助于在PCB设计通过物理测试或甚至更高级别的模拟之前优化PCB设计。

要了解更多关于SIwave的知识,请观看我们的视频YouTube频道.

Scopri cosa può票价Ansy万博s per te

Scopri cosa può票价Ansy万博s per te

Contattaci急速地

感谢你的眷顾!

我们在这里回答您的问题,并期待与您交谈。我们Ansys销售团队的一名成员万博将很快与您联系。