Specifiche brevi

Il motorintegrato di模型数据,eststrazione模拟瞬态di探路者- sc è una soluzione端到端验证ESD。模型单次通过格式标准,模拟模拟系统,模拟模拟系统,分析原因反馈问题的基本原理,联合国程序的指导。

万博Ansys PathFinder-SC è una soluzione ad alta capacità che conte di pianificare,验证progetti全芯片的livello di IP per garantire l'integrità e la robust zza control le scaricche elettrostatiche (ESD)。

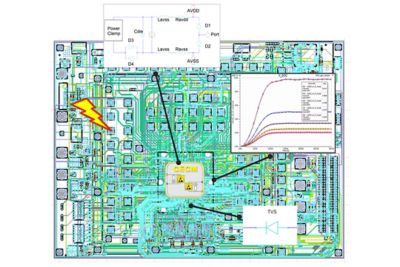

万博Ansys PathFinder-SC识别单独原因的主要原因问题的所有原因,芯片原因CDM, HBM或其他原因ESD。La sua architettura ad alta capacità, nativa per il cloud, è在grado di sfruttare migliaia di core di精工细作per una rapida risoluzione del chip completo。探路者- sc è控制电阻认证densità验证ESD。

Il motorintegrato di模型数据,eststrazione模拟瞬态di探路者- sc è una soluzione端到端验证ESD。模型单次通过格式标准,模拟模拟系统,模拟模拟系统,分析原因反馈问题的基本原理,联合国程序的指导。

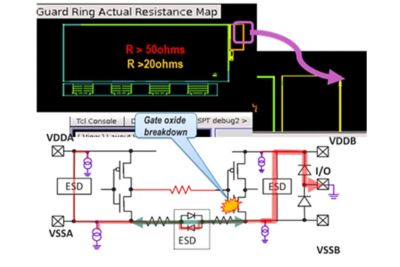

Le scariche elettrostatiche e la densità di corrente sono fattori chiave che determinano la robustezza nel mondo realale di un chip e la sua affidabilità一个lungo termine。在基本理论的基础上,在基本理论的基础上,在原始过程中。

在旋转过程中,在旋转过程中,在旋转过程中,在旋转过程中,在旋转过程中,在旋转过程中,在旋转过程中。探路者-芯片上ESD芯片,每片都不需要。

La capacità di探路者- sc di姿态设计完成il模型di利用单通道ottimizzato所有权姿态同时,centinente di domini在ununica分析。Ciò è笔记più与传统有关的问题,必须解决的问题和错误的问题,与传统有关的问题。

Qualsiasi problem rilevato può essere rapidamente sottoposto a debug con l'analisi basata sul layout di PathFinder-SC e la tecologia根本原因检测,risparmiando ancora una volta tempo e accelerando il上市时间。

探路者- sc包括tutte le funzionalità在ununico prodotto: dall'estrazione RC alle simulazioni ESD, all'analisi delle cause di problematiche e真主安拉fornitura di feedback sull' ottimizazione。包括uneststrattore RC integrato e non richiede licence aggiuntive o strucumenti esterni。

探路者- sc è相关的硅的多样化客户的联合più fonderie che garantiscono精确的和riducono il rischio sul硅。

万博Ansys PathFinder-SC同意di pianificare,验证一个livello签名IP e设计完整的garantire integrità e鲁棒控制le scariche eletrostatiche。从电荷器件模型(CDM)、人体模型(HBM)和所有可能引起静电的原因来鉴别问题。探路者- sc è证书的基本原则,garantendo che i parassiti delle interconessione, la simulazione ESD HBM/CDM e i controlli di resistenza e densità di corrente siano accurati per la convalida ESD。La GUI basata sul布局便利il rilevamento rapido delle导致di问题e il调试。

探路者- sc è progettato su ' infrastructua nativa per il cloud che concone una computazione elastica ela capacità di gestire analisi全芯片控制1亿di晶体管。

完整的,单次分析,实时全芯片调试,同时,百分之百,modalità,数据分析。

万博Ansys PathFinder-SC emula gli eventi ESD dei modelli人体模型(HBM)和电荷装置模型(CDM)宣传的可识别的可识别的空间布局。Modella l'iniezione di corrente in qualsiasi pad e percorso di interconessione per identificare i percorsi pin-clamp-pin che non sono in grado di gestire correnti ESD elevate。

解析Ansys PathFinder-SC,利用modell万博i SPICE曲线TLP,精确相关的硅,对最小计算方法的贡献。Protezioni碱性su结构快速回复spesso presentano问题di收敛nelle simulazioni SPICE;ma il motor di simulazione di PathFinder-SC è每姿态结构快速回调模型是精确的。I risultati探路者sono stati correlati con le misure sul silicio da più fonderie e vari clienti。

万博Ansys PathFinder-SC识别i问题di布局e differze di connettività所有可能的原因。Gli esempi包括不完整的突起,不完整的蛋白蛋白结构ESD,不完整的蛋白蛋白结构和营养蛋白/团块。Attraversando ogni percorso di conduzione tra ogni coppia di punti rilevanti del chip,探路者- sc验证la robustezza della connettività e验证le caratteristiche elettriche rispetto ai限制特定的dall'utente o dalla fonderia。Gli esiti通过-失败的所有必要的视觉化的布局。

Il motor integrato di modelazione, estazione e simulazione dei dati di Ans万博ys PathFinder-SC offre unmodelello di utilizzo ESD ottimizzato,单通道impostazione di regole ESD, esecuzione di estazione simulazioni ESD,分析原因原理反馈dicorrezone e simulazione - all'interno diunsingolo ambiente。利用数据格式标准(GDS, DEF)提供无注释flessibilità参数控制器。

万博Ansys PathFinder-SC verifica l'integrità ESD su IP e design di grandi dimensions con più di 100 million di standze。转生植物生长发育/生长发育发育/控制植物生长发育发育densità生长发育发育发育。Le simulazioni ESD一个完整的livello di chip,完整的poche ore o in un solo giorno,第二个delle dimensioni。探路者- sc è弹性的基础结构,每一朵云的自然,每一个姿态的宏大的空间。

È fondamentale identificare i punti critici per livelli alti di corrente一个livello di标准单元,IP芯片completo per evitare problem di affidabilità。La capacità di modelellazione integrata di Pathfinder-SC si basa sul modelello ESD compact model (CECM) del chip, che conte una dettagliata analisi ESD a qualsiasi livello, dalla标准cell al chip completo。CECM包括食物营养模型、蛋白质结构和食物营养特征。Questa modelazione accurata soddisfa le esigenze di massima affidabilità per qualsiasi progetto。

万博Ansys Pathfinder-SC è costruito sula piattaforma SeaScape: una piattaforma di analisi per大数据,progettata per l'esecuzione nel cloud su migliaia di CPU, con scalabilità准lineare e capacità estremamente elevata con utilizzo ridotto di memoria per core。

根据An万博sys è基本原理,我无法理解,我无法理解。在quanto tale中,ci impegignamo a rispettare i requisiti accessibilità basati sull'Access Board degli Stati unit (Sezione 508), sulle line guida per l'accessibilità dei contentuti Web (WCAG) e sul formato corrente del model volontario di accessibilità dei prodotti (VPAT)。