Webinar

Addressing Signal and Power Integrity Challenges of DDR5 Memory for Enabling High Speed 5G Applications

The next generation of wireless technology — driven by 5G — will transform the way we communicate, commute and collaborate with machines and humans alike in the near future. Ubiquitous connectivity, low latency and faster data rates will enable billions more smart devices. 5G will enable increased data traffic between end-user devices (including IoT) and data centers.

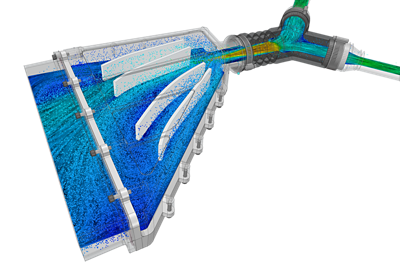

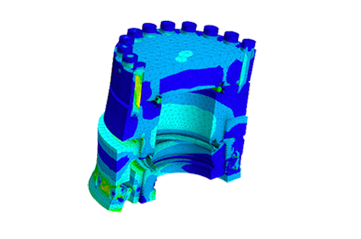

To address the high volume of data that will be generated, data centers will require increased processing speed and memory bandwidth. DDR5 memory will be a key enabler in data centers to support large data access and increased data rates for 5G applications. Meeting DDR5 signal integrity (SI) and power integrity (PI) specs will be challenging. SI and PI need to be simulated together to provide accurate results to avoid under- or over-design.

Jonghyun Cho of Rambus presented SI/PI methodologies using Ansys solutions to accurately model chip, package and board for system-level simulations. He also discussed the critical need for comprehensive chip-package-system co-analysis to meet the stringent SI/PI requirements of DDR5.