主な機能

万博Ansys VeloceRFを使用して,複数のデバイスや伝送路が密にパッキングされたデバイスを合成し,最適化されたシリコンフロアプランを実現できます。詳細なレイアウトの前に,任意の数の誘導デバイス間のカップリングを解析することで,設計サイズを縮小し,ガードリングを削減または排除します。

万博Ansys VeloceRFは誘導デバ。最小3nmという高度なノドをサポトし,主要なEDAプラットフォムと統合できます。

万博Ansys VeloceRFは,複雑なスパイラル形状のデバイスやTラインの合成とモデリングにかかる時間を大幅に短縮することで,設計サイクルを短縮します。インダクタやトランスのジオメトリをコンパイルするのに数秒しかかからず,モデリングと解析には数分しかかかりません。主要なedaプラットフォムと統合され,テプアウト可能なレアウトをンスタンス化します。

万博Ansys VeloceRFを使用して,複数のデバイスや伝送路が密にパッキングされたデバイスを合成し,最適化されたシリコンフロアプランを実現できます。詳細なレイアウトの前に,任意の数の誘導デバイス間のカップリングを解析することで,設計サイズを縮小し,ガードリングを削減または排除します。

万博Ansys VeloceRFは,複雑なスパイラル形状のデバイスやTラインの合成とモデリングにかかる時間を大幅に短縮することで,設計サイクルを短縮します。

インダクタのサイズとインダクタ間のクロストークは,ダイのサイズに影響を与える可能性があります。万博Ansys VeloceRFは、最適化条件とジオメトリ制約を使用して、より小さなデバイスを設計するのに役立ちます。さらに、任意の数のインダクタ間のカップリングを計算して、シリコン実装面積を最適化し、回路のコンテキストでインダクタを最適化します。Ansys VeloceRFでパラメトリックスイープがサポートされることで、回路のコンテキストでの最適なパフォーマンスソリューションとなります。ファウンドリ検証済みの精度により、クロストーク障害を排除するのに役立つシリコン実証済みモデルを使用して設計におけるリスクを軽減します。

万博Ansys VeloceRFは現在200を超える独自のファウンドリプロセスをサポートし,台积电社,联电社,GlobalFoundries社,TowerJazz社,三星社などのすべての半導体ファウンドリのCMOS、BiCMOS,砷化镓,SOS, SOIを含む,最小3 nmまでのあらゆるプロセスに対応しています。このルは,主要なeda設計プラットフォムおよびlvsルと統合できます。

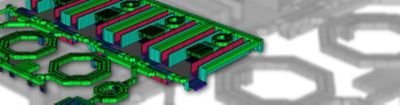

万博Ansys VeloceRFは,わずか数分で,ミリ波のスパ。drc / dfmクリンデバスを生成します。これには,最小3nmまでのフィルも含まれます。これらのデバイスは,受動性および因果律を満たす年代パラメータおよび非常にコンパクトなRLCkネットリストモデルによってモデル化され,最大限の幾何学的柔軟性をもたらすようPCell / PyCellとして提供されます。コンテキストに応じた最適化により,複数のデバイスや伝送路を密なフロアプランでパッキングすることで,ダイサイズを大幅に削減でき,ガードリングを削減または排除できます。デバイスの構成ブロックが事前定義されたライブラリで高周波をサポートし,任意の数の誘導デバイス間のカップリングをサポートします。

VeloceRFは,シリコン上の誘導デバイスの包括的な合成,モデリング,解析,および最適化を提供します。

シングルスパ▪▪ラル▪▪ンダクタ:差動型,シングルエンド,正方形および八角形,センタ,タップあり/なし

マルチスパ▪▪ラル▪▪ンダクタ:トランス,バラン,tコescル,および直列差動型

tラereplicationン:シールド付き,二重シールド,ストリップライン,カプラ,コンバイナ,およびテープアウト可能なその他のタイプ

万博Ansys VeloceRFは,任意の数のインダクタ間のカップリングを計算して,シリコン実装面積を最適化します。VeloceRFを使用して,ガードリングを締め付けたり除去したり,シリコンフロアプランを最適化したりできます。

万博Ansys VeloceRFはインダクタパラメータのパラメトリックスイープをサポートし,回路のコンテキストで最適なソリューションを提供します。これにより,インダクタ間で独自のカップリング解析が可能になり,クロストーク関連の障害を排除できます。

万博Ansys VeloceRFは,ミリ波周波数での設計に実証済みのシリコン精度をもたらします。さまざまなTライン構造で,マイクロストリップライン,コプラナーウェーブガイド(シールド付きおよび二重シールド),ストリップライン,45度および90度の曲げ,Tジャンクション,スタブ,分岐ラインカプラ,ウィルキンソン分配機など,乐高®に似た設計アプローチをサポートしています。

万博Ansys VeloceRFは現在200を超える独自のファウンドリテクノロジーをサポートし,台积电社,联电社,GlobalFoundries社,TowerJazz社,三星社などの半導体ファウンドリのあらゆるプロセス(SOI CMOS、BiCMOS,砷化镓,SOS)に対応しています。VeloceRFは,最小3nmまでのすべてのプロセスノ,ドをサポ,トします。主要なEDAプラットフォームと統合され,VeloceRFモデルは寄生成分抽出ネットリストと組み合わせることができます。

万博Ansys VeloceRFは,フル3 dメッシングアルゴリズムによって導体のボリュームが小さなセルにセグメント化される前に,レイアウト依存効果(LDE)を計算します。3d基板モデルにより,分配されたrc基板ネットワクを迅速か正確に抽出できます。抽出されたモデルは非常に正確で,電流分布,表皮効果,近接効果などの電磁現象をすべて捉えます

万博Ansysは,障害を持つユーザーを含め,あらゆるユーザーが当社製品にアクセスできることはきわめて重要であると考えています。そのため,我们访问板(508条),Web内容可访问性指南(WCAG)および自愿产品易访问性模板(VPAT)の最新フォーマットに基づくアクセシビリティ要件に準拠するよう努めています。