万博Ansys advantage杂志

日期:2020年

优化高速串行链路的串扰

作者:戴戴,美国NVIDIA圣克拉拉混合信号集成电路设计经理

今天的片上系统(SoC)设计——不管应用是什么——都在变得越来越复杂。具体来说,当涉及到根除电磁串扰并在合理的时间内实现有效的配电网络时,高速芯片变得更加令人生畏。

考虑一下,例如:

- 汽车行业的工程师们一直在为80 GHz毫米波雷达芯片而苦苦挣扎,因为芯片上的电磁器件非常复杂。当然,在终端产品安全至关重要的设备上,串扰是一个巨大的问题。

- 在5G蜂窝网络中,工程师们面临着一个电磁噩梦:同一个芯片上有很多无线电设备。一些团队必须在单个5G收发器上模拟5000种不同频率的互调产品。万博网

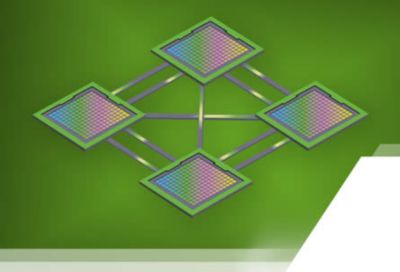

- 设计高性能人工智能芯片(如图形处理单元(gpu))的团队必须处理每秒千兆位的输入/输出以及可能产生的噪声。

- 高带宽存储器和处理器内核必须处理连接内核和存储器的复杂多层硅中间层。

所有这些芯片都有两个共同点:高速和高频。

NVIDIA的NVLink技术路线图显示,吞吐量在两年内翻了一番。紧凑的数据链路增加了串扰的风险。

当涉及到高速芯片对芯片串行链路设计时,我们的吞吐量每两年翻一番,但我们必须在相同的面积限制下做到这一点。这意味着更紧密的数据链接,这增加了串扰的风险。

此外,最新的GPU设计已广泛采用中介器。这些中介会引起额外的串扰。如果你不考虑中间插入器,它会反过来伤害你,因为中间插入器会在电感器上产生耦合。

此外,由于较大的凹凸间距(从150毫米到200毫米)和在受限区域内的有限数量的凹凸,当您想要分离噪声功率域(例如数字功率域和模拟功率域)时,这可能是一项挑战。要做到这一点,你需要多次动力和地面颠簸。当你有大量的颠簸时,很难把能量输送出去,也很难干净利落地着地。这使得相声的潜力更大。你必须分析临界质量的电力和地面的耦合是什么类型的。

知识是关键

为了提高信号完整性和功耗,我们需要了解电磁。因为我们的团队一直在推动高速、高频设计的极限,我们已经建立了一种有效、高效的方法来根除串扰问题,同时又不会阻碍我们的进度或占用太多的工程资源。

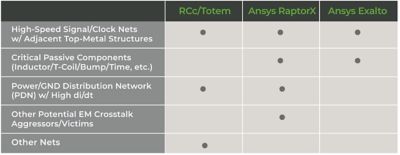

NVIDIA的设计方法是分层的。我们首先把所有东西分成不同的类别,最关键的是高速信号和时钟网络。我们从传统的电阻和电容提取耦合(RCc)提取开始,作为顶层仿真方法的一部分。在这个初步的探索中,我们不需要很多细节,但我们确实需要快速的周转时间,同时我们检查高速信号和时钟网和相邻的顶部金属结构,以及电力和地面配电网。我们转向Ansys Tot万博em,它可以进行电网弱点分析,点对点检查,以及各种早期静态和动态IR和EM分析,可以突出设计弱点。

为了对方法进行额外的分析和优化,团队依靠Ansys RaptorX和Ansys Exalto来检查高速信号和时钟网络;万博关键无源,如t型线圈、电感器和凸点;电源和地面;以及其他可能引起电磁干扰的攻击者和受害者。

RaptorX是一种布局后RLCk提取软件解决方案,使IC设计工程师能够在签署阶段准确预测电磁耦合效应。该方法通过提取集总元素寄生,捕获设计层次中不同模块间的未知串扰,生成准确的电、磁和衬底耦合模型。Exalto将上述功能与传统的RC提取流程集成在一起,使其更易于设计人员使用。

让我们看一些例子,看看我们如何在设计的各个部分实现该方法来探索串扰,并根据结果优化这些设计。

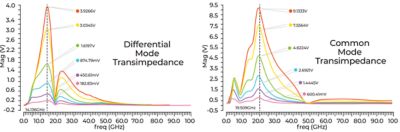

图表显示了从输电网络到敏感接收器信号网络的差分和共模串扰与有效去耦电容器的对比。图形中不同的颜色表示在配置中使用了不同数量的帽。

数据路径串扰分析

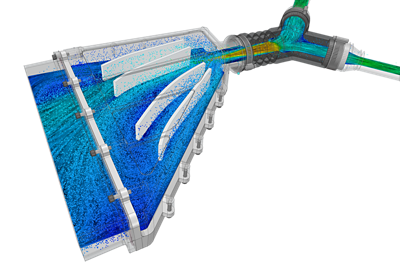

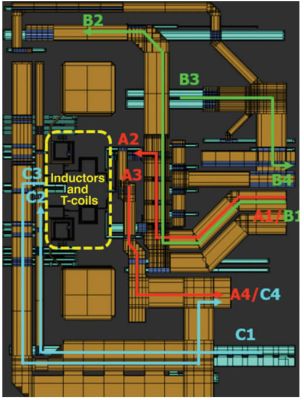

下图是最近NVIDIA GPU设计中高速接收器的部分平面图。由于面积限制和功率效率的考虑,与传统射频设计相比,电感器和t线圈具有有限的保持区域。你不能为这些无源结构提供一个大的区域,因为你将不得不把所有的高速电路分隔开。这反过来又使您的整体设计效率低下。为了捕捉相邻的串扰效果,我们使用RaptorX提取所有关键网和相邻的电源/地作为n端口,部分布局仅包括顶部的厚金属层。

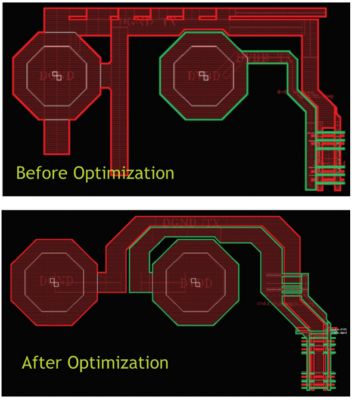

我们提取了整个区域作为模型。我们将不同的端口放置在不同的位置,并进行s参数仿真和瞬态仿真来确定串扰效果。一旦我们得到结果,我们重新优化布局和去耦电容器(decap)的位置,以尽量减少串扰效应。

我们想通过在正确的位置放置头,将感兴趣频率上的串扰效应减少2-10倍;从底部的瞬态波形可以看出,优化后的瞬态效应降低到3毫伏。它还在那里,但我们根据分析将影响降到最低。

电源时钟线路挑战

另一个大问题是从电源到高速时钟线的串扰。使用SerDes(序列化器/反序列化器)设计,通常一个锁相环(PLL)将驱动关键的高速时钟到多个不同的数据通道。根据应用程序的不同,这个时钟分布可以运行几毫米。由于面积的限制,难以避免地噪声和功率与时钟线平行运行。即使你在时钟的一侧有适当的屏蔽,这也是不够的。你仍然会感受到来自那些电线的严重的磁串扰。

为了掌握全局,您必须将多个数据通道放在一起,以包含整个时钟分布网络。要做到这一点,您需要提取50多个,有时甚至多达100个端口。只有迅猛龙才能做到这一点。

NVIDIA GPU高速接收器的局部布局图显示了片上无源元件(电感器/ t线圈)的有限保持区域。

当你用RaptorX把电源、地线和时钟全部提取出来时,你会看到电源线和地线的串扰抖动更严重。

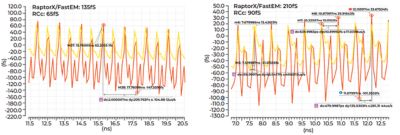

这两张对比图让NVIDIA可以观察到抖动。他们在不同的地点展示了相同的模拟。黄色的是基于碾压混凝土提取。

即使在优化之后,我们看到的瞬时抖动是仅使用rc的数字的两倍。这种影响很难完全消除,但通过适当的设置和工具,您可以预测它,并将其与其他随机抖动(RJ)和确定性抖动(DJ)一起包含在抖动预算中。如果你忽略这一点,当硅回归时,你将会有一个惊喜等着你。我们需要这个Ansys工具万博来确保我们从这种耦合中捕获所有效果。

两个比较图让NVIDIA可以观察到抖动。他们在不同的地点展示了相同的模拟。黄线是基于RCc提取。

如何优化配电

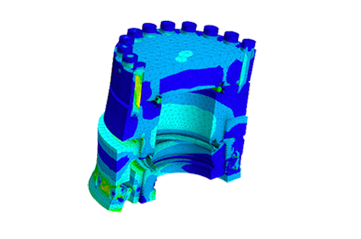

下图代表了我们使用RaptorX和Exalto组合进行的电力输送网络(PDN)优化。我们的分析既包括感应顶层金属层,也包括底部电阻下层通孔和金属层。我们把端口放在所有接入点上,包括凸起、去耦帽、电流汇和源。

该器件经过优化,可以减少对高频电流传输的长顶部金属布线的依赖,同时保持高面积效率。电流返回路径与输出路径并行精心规划,以最大限度地减少环路封闭并减少磁通/路由电感。

RaptorX使NVIDIA能够在多通道上提取长时钟路由和电力传输网络

端口数。

通过这种优化,我们能够将di/dt(电流变化率)引起的电源纹波降低40%。

规模化效率

使用先进的SerDes设计,随着频率的不断增加,通过简单的RCc提取无法捕获高速损伤。这些损害包括电磁串扰和di/dt引起的电源噪声。

NVIDIA使用Ansy万博s RaptorX和Ansys Exalto来优化电力输送网络。

我们使用RCc和EM工具的组合来正确地建模所有这些。借助RaptorX和Exalto,我们能够在短时间内高效地进行大规模提取,这使我们能够将物理设计推向极限,同时将相关风险降至最低。最终的结果是一个节能的设计。

万博Ansys가귀사를위해무엇을할수있는지알아보십시오。

万博Ansys가귀사를위해무엇을할수있는지알아보십시오。

大富豪

大黄蜂!大黄蜂!

我们在这里回答您的问题,并期待与您交谈。我们Ansys销售团队的一名成员万博将很快与您联系。